# HyperTransport<sup>™</sup> I/O Link Specification

Revision 2.00b

Document # HTC20031217-0036-0010

**4/27/2005**

#### HyperTransport Ô Technology Consortium

The HyperTransport Technology Consortium disclaims all warranties and liability for the use of this document and the information contained herein and assumes no responsibility for any errors that may appear in this document, nor does the HyperTransport Technology Consortium make a commitment to update the information contained herein.

#### **DISCLAMER**

This document is provided "AS IS" with no warranties whatsoever, including any warranty of merchantability, non-infringement, fitness for any particular purpose, or any warranty otherwise arising out of any proposal, specification or sample. The HyperTransport Technology Consortium disclaims all liability for infringement of property rights relating to the use of information in this document. No license, express, implied, by estoppels, or otherwise, to any intellectual property rights is granted herein.

#### **TRADEMARKS**

HyperTransport is a licensed trademark of the HyperTransport Technology Consortium.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

#### HyperTransport Ô Technology Consortium

#### About HyperTransport™ Technology

HyperTransport technology is a high-speed, high-performance, point-to-point link for integrated circuits, and is designed to meet the bandwidth needs of tomorrow's computing and communications platforms. HyperTransport technology helps reduce the number of buses while providing a high-performance link for PCs, workstations, and servers, as well as numerous embedded applications and highly scalable multiprocessing systems. It is designed to allow chips inside of PCs, networking and communications devices to communicate with each other up to 48 times faster than with some existing bus technologies.

#### About the HyperTransport Technology Consortium

The HyperTransport Technology Consortium is a membership-based non-profit organization in charge of managing and promoting HyperTransport Technology. It has successfully managed the swift transition of HyperTransport technology from a proprietary technology to a widely adopted and royalty-free industry standard I/O technology. HyperTransport technology is now deployed in high performance personal computers, mobile computers, servers, network equipment, communication systems and embedded products.

The HyperTransport Technology Consortium manages the HyperTransport technology specification and it promotes the business interests of consortium member companies. Consortium members include leading providers of computing, networking, communications, embedded, software and IP products and services.

The Consortium is led by founding members Advanced Micro Devices, Alliance Semiconductor, Apple Computer, Broadcom Corporation, Cisco Systems, NVIDIA, PMC-Sierra, Sun Microsystems, and Transmeta. Membership classes are based on member contribution and include five member classes with varying rights and services. Membership is open to any company interested in leveraging the HyperTransport technology. Membership is based on a minimal yearly fee and includes the right to royalty-free use of HyperTransport technology and Intellectual Property.

The Technical Working Groups, Technical Task Forces and a Marketing Working Groups are open to representatives of Promoter and Contributor member class companies and these groups manage the HyperTransport specification, drive new developments and promote the consortium.

Consortium members have access to HyperTransport technical documents database, may attend consortium meetings and events and may benefit from a variety of technical and marketing services offered by the Consortium free of charge to member companies. To learn more about member benefits and on how to become a Consortium member, visit the Consortium web page at www.hypertransport.org/cons\_join.cfm.

Before joining, please review the bylaws of the Consortium.

<u>HyperTransport is a licensed trademark of the HyperTransport Technology Consortium. All other trademarks belong to their respective owners.</u>

| REVISION | CHANGE                                                | SECTION        | DATE     |

|----------|-------------------------------------------------------|----------------|----------|

| 1.03     | Initial release                                       | All            | 10/10/01 |

| 1.04     | Fixed errata and made clarifications                  | All            | 5/30/02  |

|          | Fully defined open-drain signal behavior              | 2, 15, 18.5    |          |

|          | Document Isochronous VC limitations                   | 4.4.3, 4.4.4,  |          |

|          |                                                       | 7.5.4.9, D.1   |          |

|          | Allow RMW with count other than 1 or 3                | 4.4.5          |          |

|          | Relaxed response UnitID for rejected packets          | 4.9.3          |          |

|          | Updated upstream configuration requirements           | 4.9.4, F       |          |

|          | Swapped Interrupt and Address chapters (5 and 9)      | 5, 9           |          |

|          | Added new x86 reserved address range                  | 5              |          |

|          | Tighten Config and I/O space access requirements      | 5, B           |          |

|          | Highlighted required registers                        | 7.3-7.5        |          |

|          | Expanded description of Address registers             | 7.3.5, 7.4.6   |          |

|          | ISA and VGA enable bits required and documented       | 7.4.9.3        |          |

|          | Require a revision ID in every function               | 7.5            |          |

|          | Extend HyperTransport Capability Type field to 5 bits | 7.5.3.1, 7.7.1 |          |

|          | Documented behavior of multiple nonprefetchable       | 7.5.13         |          |

|          | memory range register extensions                      |                |          |

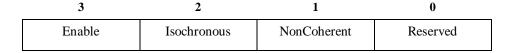

|          | Added Isochronous, NonCoherent, and Compat bits to    | 7.7            |          |

|          | Address Remapping Block                               |                |          |

|          | Created Revision ID Capability                        | 7.8            |          |

|          | Documented reset data corruption case                 | 10.1           |          |

|          | Documented behavior when all UnitIDs are consumed     | 12.3           |          |

|          | Combined Appendices B and C                           | В              |          |

|          | Relaxed PCI ordering, added HyperTransport to PCI     | B.2            |          |

|          | command mapping                                       |                |          |

|          | Added PCI-X ordering rules and command mapping        | B.4            |          |

|          | Added Deadlock Appendix C                             | C              |          |

|          | Document legacy interrupt boot requirements           | F.1            |          |

|          | Document legacy PIC multiple ExtInt requirements      | F.1.3          |          |

|          | Document delay from STOP_GRANT to LDTSTOP#            | F.2            |          |

|          | Document A20M ordering requirements                   | F.2.1.1        |          |

|          | Updated LDTREQ# requirements                          | F.2.4          |          |

|          | Updated differential signal input edge rate           | 18.10          |          |

|          | requirements                                          |                |          |

| REVISION | CHANGE                                                | SECTION             | DATE     |

|----------|-------------------------------------------------------|---------------------|----------|

| 1.05     | Added 64-bit addressing                               | 3.2.1, 4.4.6, 5,    | 11/22/02 |

|          |                                                       | 7.3.5, 7.4.6,       |          |

|          |                                                       | 7.5.4.12, 7.5.8,    |          |

|          |                                                       | 7.5.10.5, 10.1.5    |          |

|          | Changed Coherent bit from Ignored to Reserved and set | 3.2.1.5, 4.4.1      |          |

|          | Added Data Error to Responses and Posted Writes,      | 4.4.1, 4.5, 7.3,    |          |

|          | Changed Error and NXA bits in Responses to Error0/1   | 7.4, 10.2.1,        |          |

|          |                                                       | B.2.2, B.4.2        |          |

|          | Added Isoc bit to Flush and Fence                     | 4.4.3, 4.4.4, D.1   |          |

|          | Added UnitID Clumping                                 | 4.2, 4.5, 4.6, 4.9, |          |

|          |                                                       | 6.4, 7.5.10, 7.10,  |          |

|          |                                                       | 12.3                |          |

|          | Various clarifications                                | 3.2.1, 4.7, 4.9, 5, |          |

|          |                                                       | 6.1, 7.1, 8.3,      |          |

|          |                                                       | 12.2, B.2.2,        |          |

|          |                                                       | B.4.2, C.1.2        |          |

|          | Require peer-to-peer reflection of Atomic RMW         | 4.4.5               |          |

|          | Added Extended Configuration Space and Device         | 4.4.1, 4.9, 5, 7.1, |          |

|          | Messaging                                             | 7.2, 7.5.15, 7.11,  |          |

|          |                                                       | 13, B.4.2, F        |          |

|          | Restricted ordering within the chain                  | 6, 6.1              |          |

|          | Added Interrupt Disable and Status bits               | 7.3.1.6, 7.3.2.1    |          |

|          | Removed VGA Palette Snoop                             | 7.4.1               |          |

|          | Added Upstream Configuration Enable bit               | 7.5.10.8            |          |

|          | Added 64-bit Address Remapping                        | 7.8                 |          |

|          | Added INTA/B/C/D Virtual Wires                        | 8.1, 8.4            |          |

|          | Added No Snoop to HyperTransport-to-PCI-X             | B.4.2               |          |

|          | Mapping                                               |                     |          |

|          | Added Message Signaled Interrupt Mapping              | B.5                 |          |

|          | Added x86 Thermal Management Messages                 | F.2.1               |          |

|          | Relaxed x86 SMI and SMIACK Requirements               | F.2.5               |          |

|          | Added Switch Appendix                                 | 7.5.3.1, I          |          |

|          | Combined First Two Electrical Chapters                | 15                  |          |

| REVISION | CHANGE                                                      |                     |        | SECTION               | DATE    |

|----------|-------------------------------------------------------------|---------------------|--------|-----------------------|---------|

| 1.10     | Incorporated All 1.05c Errata                               | 3.2.3, 4.4.1, 4.4.5 | , 4.8. | 1, 4.9.5.2, 5, 6,     | 8/25/03 |

|          |                                                             | 6.1, 6.2, 7.3.1.4,  | 7.3.2. | 3, 7.3.2.8, 7.4.1,    |         |

|          |                                                             | 7.4.9, 7.5.3.1, 7.5 | .4, 7. | 5.5, 7.5.6, 7.5.7,    |         |

|          |                                                             | 7.5.8.3, 7.5.10.6,  | 7.5.12 | 2, 7.5.13, 7.5.14,    |         |

|          |                                                             | 7.10.2, 7.12, 8.1,  |        |                       |         |

|          |                                                             |                     |        | 10.2.4, 12.2, B.2.2,  |         |

|          |                                                             | B.4.2, B.5, F.1.1,  |        | , I.3.3.5, J, 18.7, A |         |

|          | Added Retry Mode                                            |                     |        | 1, 4.8, 7.5.3.1,      |         |

|          |                                                             |                     |        | 4.8, 7.15, 10.1.3,    |         |

|          |                                                             |                     | 10.3   |                       |         |

|          | Added New Virtual Channel Se                                | ts                  |        | 1, 4.4.1, 4.5, 4.7,   |         |

|          |                                                             |                     |        | 2, 4.9.7, 6.1,        |         |

|          |                                                             |                     |        | 3.1, 7.14, 10.1.5     |         |

|          | Added DirectRoute Peer-to-Pee                               | r Routing           |        | 4.2, 4.9, 6,          |         |

|          |                                                             |                     |        | 3.1, 7.5.3.2.4, 7.13  |         |

|          | Added Streaming Packets                                     | 1                   | 14     |                       |         |

|          | Added End-to-End Flow Contro                                |                     | K      |                       |         |

| 2.00     | Various Editorial and Typograp                              |                     | All    |                       | 2/0/04  |

| 2.00     | Added PCI Express Ordering R                                | ules and            | B.6    |                       | 2/9/04  |

|          | Command Mappings                                            | 1                   | 7.5    | 7 15 17 10 10         |         |

|          | Added 2, 2.4, and 2.8GT/s Elect                             | tricais             |        | 7, 15, 17, 18, 19,    |         |

|          | Added Fixed MSI Manning Con                                 | a hility            | 7.12   | L, M                  |         |

|          | Added Fixed MSI Mapping Cap Added Translation Permitted bit | -                   |        | B.4.2                 |         |

|          |                                                             |                     | 13, 1  | D.4.2                 |         |

|          | Express Message interoperabilit<br>Errata                   | .y.                 | 7 12   | , 8.4, B.2.2, B.4.2,  |         |

|          | Errata                                                      |                     | C.1.   |                       |         |

|          | Relaxed Host and Bridge orderi                              | na requirements     | 6.1    | 2                     |         |

|          | Relaxed End of Chain bit requir                             |                     | 7.5.4  | 1.6                   |         |

|          | Various Editorial and Typograp                              |                     | 1      | 1, 4.7.10, 4.8.2, 6,  |         |

|          | , anous Editorial and Typograp                              | mean Corrections    |        | 4.6, 7.14             |         |

| 2.00a    | Removed unnecessary 1us delay                               | y from LDTSTOP      |        | 10.3.12               | 7/8/04  |

|          | disconnect in retry mode                                    |                     |        |                       |         |

|          | Clarified per-packet CRC polari                             | ity and usage       |        | 10.3.3                |         |

|          | Clarified scope of Interrupt Disa                           | able bit            |        | 7.3.1.6               |         |

|          | Clarified INTx chain host state                             | requirements        |        | 8.4                   |         |

|          | Clarified Bridge Bit and UnitID                             | in DirectRoute      |        | 4.2, 4.9, 7.13.1.6    |         |

|          | Clarified SYNC detection in Re                              |                     |        | 10.3.7                |         |

|          | Clarified LDTSTOP sequence in                               | n Retry Mode        |        | 10.3.12               |         |

|          | Corrected nonvectored interrupt                             |                     |        | F.1.1                 |         |

|          | Clarified replay ordering/buffer                            | issues in Retry Mo  | ode    | 10.3.5, 10.3.10       |         |

| REVISION | CHANGE                                                | SECTION         | DATE            |

|----------|-------------------------------------------------------|-----------------|-----------------|

| 2.00b    | Remove Interrupt Capability requirement               | 7.6, 9          | <u>4/27</u> /05 |

|          | Clarify Disconnect NOP insertion for LDTSTOP          | 8.3             |                 |

|          | Allow protocol error logging in Retry Mode            | 10.3.3, 10.3.7  |                 |

|          | Clarify stomped packet behavior in Retry Mode         | 10.3.4, 10.3.7  |                 |

|          | Clarify RxNextPktToAck behavior                       | 10.3.5          |                 |

|          | Restrict control packet insertion                     | 10.3.6          |                 |

|          | Allow new packets during history structure replay     | 10.3.10         |                 |

|          | Clarify transmitter disconnect and reconnect behavior | 10.3.12         |                 |

|          | in Retry Mode                                         |                 |                 |

|          | Fix chain bit in PCI-X and PCI-Express Mappings       | B.4.2, B.6.2    |                 |

|          | Clarify Unsupported Request and Completer Abort       | B.6.2           |                 |

|          | mapping and No Snoop bit handling in PCI-Express      |                 |                 |

|          | Correct Data Error handling in PCI-Express            | B.6.2           |                 |

|          | Fix formatting and typographical errors               | 3.2.1.5, 7.12,  |                 |

|          |                                                       | 10.1.5, 13, F.2 |                 |

| L | ist of I | Tigures                                                             | 21 |

|---|----------|---------------------------------------------------------------------|----|

| L | ist of T | Cables                                                              | 23 |

| P | reface   |                                                                     | 29 |

|   | This I   | Document                                                            | 29 |

|   | Orgai    | nization                                                            | 29 |

| S | Sec      | tion 1 – Protocol                                                   | 29 |

| 1 |          | Overview                                                            |    |

|   | 1.1      | Terminology                                                         |    |

|   | 1.2      | HyperTransport™ Technology in x86 Platforms                         |    |

| 2 |          | Signaling                                                           |    |

| 3 |          | Packet Definition                                                   |    |

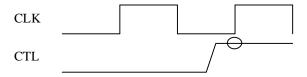

|   | 3.1      | Use of the CTL Signal                                               | 34 |

|   | 3.2      | Packet Structure                                                    | 35 |

|   | 3.2      | .1 Control Packets                                                  | 35 |

|   | 3.2      | .2 Data Packet                                                      | 41 |

|   | 3.2      | .3 Note about VC Stalls due to Command-Data Separation              | 42 |

| 4 |          | Fabric Operation                                                    | 43 |

|   | 4.1      | Topology                                                            | 43 |

|   | 4.1      | .1 Double-Hosted Chains                                             | 45 |

|   | 4.1      | .2 HyperTransport <sup>TM</sup> Technology Signals PWROK and RESET# | 46 |

|   | 4.2      | Transactions and UnitID                                             | 47 |

|   | 4.3      | Link Synchronization                                                | 48 |

|   | 4.4      | Requests                                                            | 48 |

|   | 4.4      | .1 Sized Reads and Writes                                           | 48 |

|   | 4.4      | .2 Broadcast Message                                                | 51 |

|   | 4.4      | .3 Flush                                                            | 52 |

|   |          |                                                                     |    |

| 4.4 | 1.4  | Fence                           | .53  |

|-----|------|---------------------------------|------|

| 4.4 | 1.5  | Atomic Read-Modify-Write        | . 54 |

| 4.4 | 1.6  | Address Extension               | . 55 |

| 4.5 | Resp | ponses                          | . 56 |

| 4.5 | 5.1  | Read Response (RdResponse)      | . 56 |

| 4.5 | 5.2  | Target Done (TgtDone)           | . 57 |

| 4.6 | I/O  | Streams                         | . 58 |

| 4.6 | 5.1  | UnitID Clumping                 | . 59 |

| 4.7 | Virt | ual Channels                    | . 60 |

| 4.7 | 7.1  | Virtual Channel Set Definitions | . 60 |

| 4.7 | 7.2  | The Base VC Set                 | . 62 |

| 4.7 | 7.3  | The Isoc VC Set                 | . 63 |

| 4.7 | 7.4  | The AltSet VCs                  | . 63 |

| 4.7 | 7.5  | The Non-FC-Isoc VC              | . 63 |

| 4.7 | 7.6  | The StreamVC Set                | . 63 |

| 4.7 | 7.7  | VCSets 3 and 5                  | . 64 |

| 4.7 | 7.8  | VCSet 4                         | . 64 |

| 4.7 | 7.9  | VCSet 6-7                       | . 64 |

| 4.7 | 7.10 | Interworking Between Revisions  | . 64 |

| 4.7 | 7.11 | Added VCSet Considerations      | . 65 |

| 4.8 | Flov | v Control                       | . 65 |

| 4.8 | 3.1  | NOP Flow Control Packet         | . 65 |

| 4.8 | 3.2  | Extended Flow Control Packet    | . 68 |

| 4.9 | Rou  | ting                            | . 70 |

| 4.9 | 9.1  | Acceptance                      | . 70 |

| 4.9 | 9.2  | Forwarding                      | . 70 |

| 4.9 | 9.3  | Rejection                       | .71  |

| 4.9 | 9.4  | Host Bridges                    | .72  |

| 4.9 | 9.5  | Fairness and Forward Progress.  | .73  |

| 4.9 | 9.6  | DirectRoute Routing             | . 75 |

|     |      |                                 |      |

### HyperTransport™ I/O Link Specification Revision 2.00b

|   | 4.9.7   | VCSet Arbitration                                                                        | .77  |

|---|---------|------------------------------------------------------------------------------------------|------|

| 5 | Ado     | dressing                                                                                 | .79  |

| 6 | I/O     | Ordering                                                                                 | .81  |

|   | 6.1 Ups | tream I/O Ordering                                                                       | . 82 |

|   | 6.2 Hos | t Ordering Requirements                                                                  | . 85 |

|   | 6.2.1   | Host Responses to Nonposted Requests                                                     | .86  |

|   | 6.3 Dov | vnstream I/O Ordering                                                                    | . 87 |

|   | 6.4 Ord | ering in Sharing Double-Hosted Chains                                                    | . 87 |

| 7 | Cor     | nfiguration Accesses                                                                     | .88  |

|   | 7.1 Con | figuration Cycle Types                                                                   | .88  |

|   | 7.2 Con | figuration Space Mapping                                                                 | .90  |

|   | 7.2.1   | Function and Register Numbering.                                                         | .90  |

|   | 7.2.2   | Device Numbering                                                                         | .90  |

|   | 7.2.3   | Bus Numbering                                                                            | .91  |

|   | 7.2.4   | Software View of Extended Configuration Space                                            | .91  |

|   | 7.3 Hyp | erTransport <sup>TM</sup> Technology Device Header                                       | .91  |

|   | 7.3.1   | Command Register: Offset 04h                                                             | .92  |

|   | 7.3.2   | Status Register: Offset 06h                                                              | .93  |

|   | 7.3.3   | Cache Line Size Register: Offset 0Ch: R/O                                                | .95  |

|   | 7.3.4   | Latency Timer Register: Offset 0Dh: R/O                                                  | .95  |

|   | 7.3.5   | Base Address Registers (BARs): Offsets 10-24h: R/W: Warm Reset                           | .95  |

|   | 7.3.6   | CardBus CIS Pointer: Offset 28h: R/O                                                     | .96  |

|   | 7.3.7   | Capabilities Pointer: Offset 34h: R/O                                                    | .96  |

|   | 7.3.8   | Interrupt Line Register: Offset 3Ch: R/W: Warm Reset                                     | .96  |

|   | 7.3.9   | Interrupt Pin Register: Offset 3Dh: R/O                                                  | .96  |

|   | 7.3.10  | Min_Gnt, and Max_Lat Registers: Offsets 3E and 3Fh: R/O                                  | .96  |

|   | 7.4 Hyp | erTransport <sup>TM</sup> Technology Bridge Headers                                      | .97  |

|   | 7.4.1   | Command Register: Offset 04h                                                             | .98  |

|   | 7.4.2   | Status, Primary Latency Timer, Base Address, Interrupt Pin, and Interrupt Line Registers |      |

|   | 7.4.3   | Cache Line Size: Offset 0Ch: R/O                                                         | .99  |

# HyperTransport<sup>TM</sup> I/O Link Specification Revision 2.00b

| 7.4.4    | Secondary Latency Timer Register: Offset 1Bh: R/O                                        | .99 |

|----------|------------------------------------------------------------------------------------------|-----|

| 7.4.5    | Secondary Status Register: Offset 1Eh                                                    | 99  |

| 7.4.6    | Memory and Prefetchable Memory Base and Limit Registers: Offsets 20-2Ch: R/W: Warm Reset |     |

| 7.4.7    | I/O Base and Limit Registers: Offsets 1C, 1D, 30, and 32h: R/W: Warm Reset               | 101 |

| 7.4.8    | Capabilities Pointer Register: Offset 34h: R/O                                           | 102 |

| 7.4.9    | Bridge Control Register: Offset 3Eh                                                      | 102 |

| 7.5 Cap  | pability Registers                                                                       | 104 |

| 7.5.1    | Capability ID: Offset 00h: R/O                                                           | 106 |

| 7.5.2    | Capabilities Pointer: Offset 01h: R/O                                                    | 106 |

| 7.5.3    | Command Register: Offset 02h                                                             | 106 |

| 7.5.4    | Link Control Register: Offsets 04h and 08h                                               | 110 |

| 7.5.5    | Link Configuration Register: Offsets 06h and 0Ah                                         | 114 |

| 7.5.6    | Revision ID Register: Offset 08h or 0Ch: R/O                                             | 116 |

| 7.5.7    | Link Frequency Register: Offsets 09h or 0Dh and 11h (Bits 3:0): R/W: Cold Reset to 0     |     |

| 7.5.8    | Link Error Register: Offsets 09h or 0Dh and 11h (Bits 7:4)                               | 119 |

| 7.5.9    | Link Frequency Capability Register: Offsets 0Ah or 0Eh and 12h: R/O                      | 119 |

| 7.5.10   | Feature Capability Register: Offset 0Ch or 10h                                           | 120 |

| 7.5.11   | Enumeration Scratchpad Register: Offset 10h or 14h: R/W: Cold Reset to 0                 | 122 |

| 7.5.12   | Error Handling Register: Offset 12h or 16h                                               | 122 |

| 7.5.13   | Memory Base Upper 8 Bits: Offset 14h or 18h: R/W: Warm Reset to 0                        | 125 |

| 7.5.14   | Memory Limit Upper 8 Bits: Offset 15h or 19h: R/W: Warm Reset to 0                       | 125 |

| 7.5.15   | Bus Number: Offset 1Ah: R/O: Warm Reset to 0                                             | 125 |

| 7.6 Inte | errupt Discovery and Configuration Capability Block                                      | 125 |

| 7.6.1    | Last Interrupt: Index 01h: R/O                                                           | 126 |

| 7.6.2    | Interrupt Definition Registers: Index 10h and Higher: Warm Reset                         | 126 |

| 7.7 401  | bit Address Remapping Capability Block                                                   | 127 |

| 7.7.1    | Capability Header                                                                        | 128 |

| 7.7.2    | Secondary Bus Window Control Registers: R/W: Warm Reset to 0                             | 129 |

| 7.7.3    | Secondary Bus Window Base Registers: R/W: Warm Reset to 0                                | 129 |

|          |                                                                                          |     |

### HyperTransport™ I/O Link Specification Revision 2.00b

|                        | 7.7.4  |      | DMA Window Control Register: R/W: Warm Reset to 0              | 129 |

|------------------------|--------|------|----------------------------------------------------------------|-----|

|                        | 7.7.5  |      | DMA Primary Base Register: R/W: Warm Reset to 0                | 130 |

|                        | 7.7.6  |      | DMA Secondary Base and Limit Registers: R/W: Warm Reset to 0   | 130 |

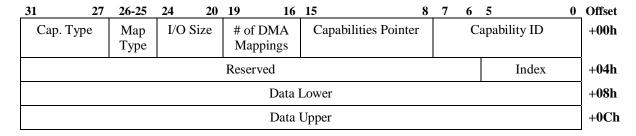

|                        | 7.8    | 64 b | oit Address Remapping Capability                               | 130 |

|                        | 7.8.   | 1    | Capability Header                                              | 130 |

|                        | 7.8.   | 2    | Index and Data Registers                                       | 131 |

|                        | 7.9    | Rev  | ision ID Capability                                            | 132 |

|                        | 7.10   | Unit | ID Clumping Capability                                         | 133 |

|                        | 7.10   | ).1  | UnitID Clumping Support (Offset 4h): R/O                       | 133 |

|                        | 7.10   | 0.2  | UnitID Clumping Enable (Offset 8h): R/W: Warm Reset to 0       | 134 |

|                        | 7.11   | Exte | ended Configuration Space Access Capability                    | 134 |

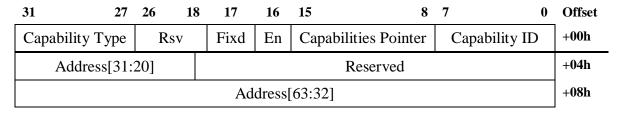

|                        | 7.12   | MSI  | Mapping Capability                                             | 135 |

|                        | 7.13   | Dire | ectRoute Capability                                            | 136 |

|                        | 7.13   | 3.1  | Capability Header                                              | 136 |

|                        | 7.13.2 |      | DirectRoute Base/Limit Registers                               | 137 |

|                        | 7.14   | VCS  | Set Capability                                                 | 138 |

|                        | 7.14   | 1.1  | Capability Header                                              | 138 |

|                        | 7.15   | Erro | or Retry Capability                                            | 140 |

|                        | 7.15   | 5.1  | Capability Registers R/O                                       | 140 |

|                        | 7.15   | 5.2  | Control Register                                               | 140 |

|                        | 7.15   | 5.3  | Status Register                                                | 141 |

|                        | 7.15   | 5.4  | Retry Count: R/W: Cold Reset to 0                              | 142 |

| 8                      |        | Sys  | tem Management                                                 | 143 |

|                        | 8.1    | Con  | nmand Mapping                                                  | 143 |

|                        | 8.2    | Spec | cial Cycles                                                    | 145 |

|                        | 8.3    | Disc | connecting and Reconnecting HyperTransport <sup>TM</sup> Links | 145 |

|                        | 8.4    | INT  | x Virtual Wire Messages                                        | 148 |

|                        | 8.5    | INT  | _Pending Message                                               | 149 |

| 9                      |        | Inte | errupts                                                        | 151 |

| 9.1 Interrupt Requests |        | Inte | rrupt Requests                                                 | 151 |

### HyperTransport™ I/O Link Specification Revision 2.00b

| 9.2  | End    | of Interrupt (EOI)                                   | 152 |

|------|--------|------------------------------------------------------|-----|

| 10   | Err    | or Handling                                          | 154 |

| 10.1 | Erro   | or Conditions                                        | 154 |

| 10   | 0.1.1  | Transmission Errors: 8-Bit, 16-Bit, and 32-Bit Links | 154 |

| 10   | 0.1.2  | Transmission Errors: 2-Bit and 4-Bit Links           | 156 |

| 10   | 0.1.3  | Protocol Errors.                                     | 157 |

| 10   | 0.1.4  | Receive Buffer Overflow Errors.                      | 158 |

| 10   | 0.1.5  | End of Chain Errors                                  | 158 |

| 10   | 0.1.6  | Chain Down Errors                                    | 159 |

| 10   | 0.1.7  | Response Errors.                                     | 159 |

| 10.2 | 2 Erro | or Reporting                                         | 159 |

| 10   | 0.2.1  | Error Responses                                      | 160 |

| 10   | 0.2.2  | Data Error in Posted Requests                        | 160 |

| 10   | 0.2.3  | Error Interrupts                                     | 161 |

| 10   | 0.2.4  | Sync Flooding                                        | 161 |

| 10   | 0.2.5  | Error Routing CSRs                                   | 163 |

| 10.3 | B Erro | or Retry Protocol                                    | 163 |

| 10   | 0.3.1  | Overview                                             | 163 |

| 10   | 0.3.2  | Retry Mode Entry and Exit                            | 164 |

| 10   | 0.3.3  | Per-Packet CRC                                       | 164 |

| 10   | 0.3.4  | Speculative Forwarding and Stomping                  | 167 |

| 10   | 0.3.5  | Packet History and Acknowledgement                   | 168 |

| 10   | 0.3.6  | Control Packet Insertion.                            | 170 |

| 10   | 0.3.7  | Receiver Requirements                                | 170 |

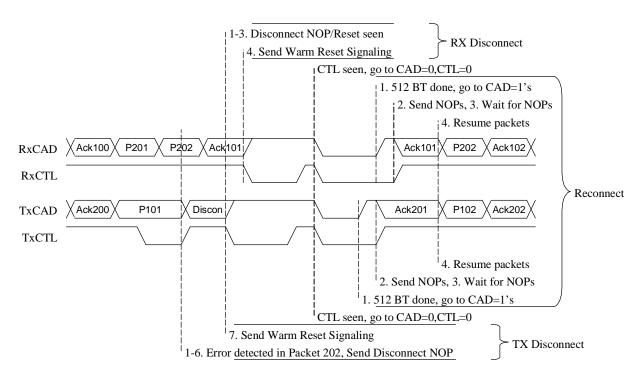

| 10   | 0.3.8  | Transmitter Disconnect                               | 171 |

| 10   | 0.3.9  | Receiver Disconnect                                  | 172 |

| 10   | 0.3.10 | Reconnection                                         | 172 |

| 10   | 0.3.11 | Multiple Retry Attempts                              | 173 |

| 10   | 0.3.12 | LDTSTOP# Sequence                                    | 174 |

| 10   | 0.3.13 | Reporting an Unrecoverable Link Error                | 175 |

|      |        |                                                      |     |

| 10       | 3.14 Retry Logging and Statistics                        | 176 |

|----------|----------------------------------------------------------|-----|

| 11       | Clocking                                                 | 177 |

| 11.1     | Clocking Mode Definitions                                | 177 |

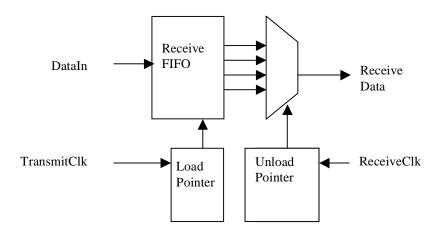

| 11.2     | Receive FIFO                                             | 178 |

| 11.3     | Async Mode Implementation Example                        | 179 |

| 11.4     | Link Frequency Initialization and Selection              | 179 |

| 12       | Reset and Initialization                                 | 180 |

| 12.1     | Definition of Reset                                      | 180 |

| 12.2     | System Powerup, Reset, and Low-Level Link Initialization | 180 |

| 12.3     | I/O Chain Initialization                                 | 185 |

| 12.      | 3.1 Finding the Firmware ROM                             | 187 |

| 12.4     | Link Width Initialization                                | 187 |

| 12.5     | 5 Link Frequency Initialization                          | 188 |

| 13       | Device Messaging                                         | 189 |

| 14       | Streaming Packet                                         | 193 |

| 14.1     | Streaming Semantics                                      | 193 |

| 14.2     | Streaming Message Segmentation                           | 193 |

| 14.3     | End Device Responsibilities                              | 194 |

| 14.4     | Streaming Request Packet Format                          | 195 |

| Protocol | l Appendices                                             | 197 |

| A        | Address Remapping Capability                             | 197 |

| A.1      | I/O Space Aliasing                                       | 197 |

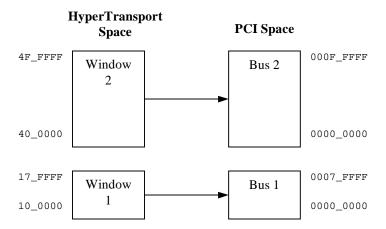

| A.2      | Memory Space Mapping                                     | 198 |

| A.3      | DMA Window Remapping                                     | 198 |

| В        | Ordering Rules and Mapping of Other I/O Protocols        | 200 |

| B.1      | Processors                                               | 200 |

| B.2      | PCI                                                      | 201 |

| B.2      | 2.1 Ordering                                             | 201 |

| B.2      | 2.2 Command Mapping                                      | 202 |

| B.3      | AGP                                                      | 203 |

### HyperTransport™ I/O Link Specification Revision 2.00b

| B.3   | 3.1  | Ordering                                     | 203 |

|-------|------|----------------------------------------------|-----|

| B.3.2 |      | Command Mapping                              | 204 |

| B.4   | PCI  | -X                                           | 207 |

| B.4   | 1.1  | Ordering                                     | 207 |

| B.4   | 1.2  | Command Mapping                              | 208 |

| B.5   | Mes  | sage Signaled Interrupts                     | 213 |

| B.6   | PCI  | Express                                      | 214 |

| В.6   | 5.1  | Ordering                                     | 214 |

| В.6   | 5.2  | Command Mapping                              | 215 |

| В.6   | 5.3  | System Management Considerations             | 218 |

| C     | Sun  | nmary of Deadlock Scenarios                  | 220 |

| C.1   | Refl | lection/Forwarding Loops                     | 220 |

| C.1   | 1.1  | Problem                                      | 220 |

| C.1   | 1.2  | Solution 1: Avoidance                        | 221 |

| C.1   | 1.3  | Solution 2: Switching Channels               | 222 |

| C.1   | 1.4  | Solution 3: Modifying Requests               | 222 |

| C.2   | Pacl | ket Issue and Acceptance                     | 223 |

| C.2   | 2.1  | Control/Data Buffer Dependency               | 223 |

| C.2   | 2.2  | Response Buffer Dependency                   | 223 |

| C.2   | 2.3  | Posted Request Acceptance                    | 224 |

| C.3   | Lega | acy Buses                                    | 224 |

| C.3   | 3.1  | Host/DMA Deadlock                            | 224 |

| C.3   | 3.2  | Peer-to-Peer Deadlock                        | 224 |

| C.4   | Syst | tem Management                               | 225 |

| C.5   | PCI  | Requirements.                                | 225 |

| C.5   | 5.1  | Posted Requests Must Pass Nonposted Requests | 225 |

| C.5   | 5.2  | Responses Must Pass Nonposted Requests       | 227 |

| C.5   | 5.3  | Posted Requests Must Pass Responses          | 227 |

| D     | Cor  | nsiderations for Isochronous Traffic         | 228 |

| D.1   | Isoc | chronous Flow Control Mode (Optional)        | 228 |

|       | D.2                                  | Normal Flow Control Mode        |                                                           |       |  |  |

|-------|--------------------------------------|---------------------------------|-----------------------------------------------------------|-------|--|--|

| E     | Southbridges and Compatibility Buses |                                 |                                                           |       |  |  |

|       | E.1 ISA/LPC Deadlock Case            |                                 |                                                           | . 230 |  |  |

|       | E.2                                  | E.2 ISA/LPC Write Post Flushing |                                                           |       |  |  |

|       | E.3                                  | Subt                            | ractive Decoding                                          | . 231 |  |  |

|       | E.3.                                 | 1                               | Subtractive Decode in the General Case                    | . 231 |  |  |

|       | E.3.                                 | 2                               | Subtractive Decode in x86 Legacy Systems                  | . 231 |  |  |

|       | E.3.                                 | 3                               | Subtractive Decode in the Simplest Case                   | . 232 |  |  |

|       | E.3.                                 | 4                               | Subtractive Decode Behind a PCI Bridge                    | . 232 |  |  |

|       | E.4                                  | VGA                             | A Palette Snooping                                        | . 233 |  |  |

| F     |                                      | Req                             | uired Behavior in x86 Platforms                           | 234   |  |  |

|       | F.1                                  | Inter                           | тupts                                                     | . 234 |  |  |

|       | F.1.                                 | 1                               | Interrupt Request                                         | . 235 |  |  |

|       | F.1.                                 | 2                               | Standard EOI                                              | . 238 |  |  |

| F.1.3 |                                      | 3                               | Legacy PIC (8259) Interrupt Request, Acknowledge, and EOI | . 238 |  |  |

|       | F.1.                                 | 4                               | Alternate Interrupt Discovery and Configuration Mechanism | . 239 |  |  |

|       | F.2                                  | Syst                            | em Management                                             | . 240 |  |  |

|       | F.2.                                 | 1                               | Command Encoding                                          | . 243 |  |  |

|       | F.2.                                 | 2                               | VID/FID Changes                                           | . 246 |  |  |

|       | F.2.                                 | 3                               | Throttling                                                | . 246 |  |  |

|       | F.2.                                 | 4                               | C3 System State Transitions and LDTREQ#                   | . 247 |  |  |

|       | F.2.                                 | 5                               | SMI and STPCLK.                                           | . 247 |  |  |

|       | F.2.                                 | 6                               | Default State of Virtual Wires                            | . 248 |  |  |

|       | F.3                                  | Initi                           | alization Issues                                          | . 248 |  |  |

|       | F.4                                  | AGI                             | P Bridge Issues                                           | . 248 |  |  |

|       | F.5                                  | Con                             | figuration Space Access Mechanism                         | . 249 |  |  |

| G     |                                      | CR                              | C Testing Mode                                            | . 250 |  |  |

| H     |                                      | Dou                             | bleword-Based Data Buffer Flow Control                    | . 251 |  |  |

| I     |                                      | Swi                             | tches                                                     | . 253 |  |  |

|       | I.1                                  | Ove                             | rview                                                     | . 253 |  |  |

|       |                                      |                                 |                                                           |       |  |  |

|    | I.1.1            | 1 Definitions                                    |     |  |

|----|------------------|--------------------------------------------------|-----|--|

|    | I.2              | Operation                                        | 255 |  |

|    | I.2.1            | Ports                                            | 255 |  |

|    | I.2.2 Partitions |                                                  |     |  |

|    | I.2.3            | Compatibility Accesses                           | 257 |  |

|    | I.2.4            | Configuration Accesses                           | 257 |  |

|    | I.2.5            | Packet and Event Routing                         | 258 |  |

|    | I.2.6            | LDTSTOP# and LDTREQ#                             | 272 |  |

|    | I.2.7            | Error management                                 | 272 |  |

|    | I.2.8            | Cascading Switches                               | 273 |  |

|    | I.2.9            | Topology and Ordering Considerations             | 273 |  |

|    | I.2.1            | 0 Hot Plug                                       | 274 |  |

|    | I.2.1            | 1 Virtual Tunnels                                | 274 |  |

|    | I.2.1            | 2 Port Splitting                                 | 274 |  |

|    | I.3              | Switch Configuration.                            | 275 |  |

|    | I.3.1            | Bridge Headers                                   | 275 |  |

|    | I.3.2            | Interface Capability Blocks                      | 275 |  |

|    | I.3.3            | Switch Capability Block                          | 276 |  |

|    | I.4              | Switch Requirements for x86 Systems              | 282 |  |

| J  |                  | Quick Reference for x86 Systems                  | 283 |  |

| K  |                  | End-to-End Flow Control                          | 285 |  |

|    | K.1              | Description of End to End Flow Control           | 285 |  |

|    | K.2              | Streaming End-to-End Flow Control Request Format | 285 |  |

|    | K.3              | End System Responsibilities                      | 287 |  |

| S  | ect              | ion 2 – Electrical Interface                     | 289 |  |

| 15 |                  | HyperTransport <sup>TM</sup> Link Overview       | 289 |  |

| 16 |                  | Supply Characteristics                           | 293 |  |

| 17 |                  | Power Requirements                               |     |  |

| 18 |                  | Input/Output DC Voltage Characteristics          | 295 |  |

|    | 18.1             | Impedance Requirements                           | 295 |  |

| 18.2                                         | DC     | Output Voltage Requirements           | . 296 |

|----------------------------------------------|--------|---------------------------------------|-------|

| 18.2.1 ATE Test Environment                  |        | . 296                                 |       |

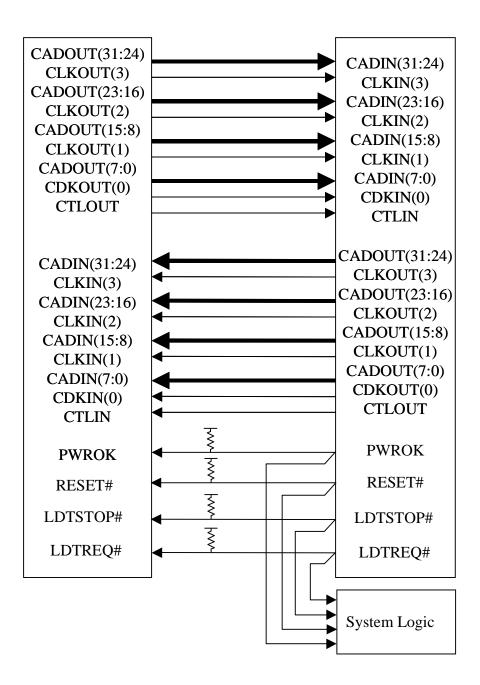

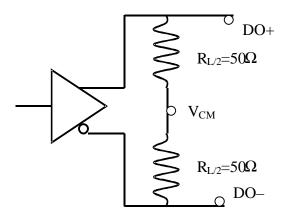

| 18.2.2 R                                     |        | Reference System Load                 | . 296 |

| 18.2.3 Output Voltage Parameter Descriptions |        |                                       | . 297 |

| 18.3                                         | DC     | Input Requirements                    | . 298 |

| 18                                           | .3.1   | ATE Test Environment                  | . 298 |

| 18                                           | .3.2   | Input Parameter Descriptions          | . 298 |

| 18.4                                         | Diff   | Perential Signal DC Specifications    | . 299 |

| 18.5                                         | Sing   | gle-Ended Signal AC/DC Specifications | 300   |

| 18.6                                         | Inpu   | nt/Output AC Voltage Characteristics  | 300   |

| 18.7                                         | Imp    | edance Requirements                   | 301   |

| 18.8                                         | AC     | Output Requirements                   | . 303 |

| 18                                           | .8.1   | ATE Test Environment                  | . 303 |

| 18                                           | .8.2   | Reference System Load                 | . 303 |

| 18                                           | .8.3   | Output Parameter Descriptions         | . 303 |

| 18.9                                         | AC     | Input Requirements                    | . 305 |

| 18                                           | .9.1   | ATE Test Environment                  | . 305 |

| 18                                           | .9.2   | Input Parameter Descriptions          | . 305 |

| 18.1                                         | 0 Diff | Perential Signal AC Specifications    | . 306 |

| 19                                           | Lin    | k Transfer Timing Characteristics     | 307   |

| 19.1                                         | Sign   | nal Groups                            | . 308 |

| 19.2                                         | Dev    | ice Output Timing Characteristics     | . 309 |

| 19                                           | .2.1   | Differential Output Skew              | . 309 |

| 19                                           | .2.2   | $T_{CADV}(T_{CADValid})$              | . 309 |

| 19.3                                         | Dev    | ice Input Timing Characteristics      | 310   |

| 19                                           | .3.1   | Input Differential Skew               | 310   |

| 19                                           | .3.2   | T <sub>SU</sub> and T <sub>HD</sub>   | .311  |

| 19.4                                         | Inte   | rconnect Timing Characteristics       | . 312 |

| 19                                           | .4.1   | T <sub>CADVRS/RH</sub>                | .312  |

| 19.5                                         | Trai   | nsfer Timing Characteristics          | . 313 |

|                                              |        |                                       |       |

| 20 Phase Recovery Timing Characteristics |        |                                                                     | 315 |  |  |

|------------------------------------------|--------|---------------------------------------------------------------------|-----|--|--|

| 20.1                                     | Red    | ceiver Modes of Operation                                           | 316 |  |  |

| 20.1.1 Synchronous Operation             |        | 316                                                                 |     |  |  |

| 20                                       | .1.2   | Pseudo Synchronous Operation                                        | 316 |  |  |

| 20                                       | .1.3   | Asynchronous Operation                                              | 316 |  |  |

| 20.2                                     | Pha    | ase Recovery Timing Variations                                      | 317 |  |  |

| 20                                       | .2.1   | Uncertainty When Initializing the Pointers                          | 317 |  |  |

| 20                                       | .2.2   | Other Factors Affecting FIFO Size and Read Pointer Separation       | 318 |  |  |

| 20.3                                     | Pha    | ase Recovery Timing Characteristics                                 | 319 |  |  |

| 20.4                                     |        | conciling Phase Recovery Timing to Receiver FIFO Depth and Read Po- |     |  |  |

| 20                                       | .4.1   | Read Pointer Initialization                                         | 321 |  |  |

| 20                                       | .4.2   | Minimum FIFO Depth                                                  | 321 |  |  |

| Electri                                  | cal In | terface Appendices                                                  | 322 |  |  |

| L                                        | DC     | C and AC Characteristics and Relationships                          | 322 |  |  |

| L.1                                      | DC     | Parameters                                                          | 322 |  |  |

| L.2                                      | Rel    | lationships Between AC and DC Parameters                            | 323 |  |  |

| L.3                                      | Rel    | lationships Between Output and Input Parameters                     | 323 |  |  |

| M                                        | Pa     | ckage and PCB Skew Assumptions                                      | 324 |  |  |

| M.1                                      | Tra    | nsmitter and Receiver Package Skew                                  | 324 |  |  |

| M.2                                      | PC     | C                                                                   |     |  |  |

#### HyperTransport™ I/O Link Specification Revision 2.00b

# **List of Figures**

| Figure 1.  | HyperTransport <sup>TM</sup> I/O Link          |

|------------|------------------------------------------------|

| Figure 2.  | Example Device Configurations                  |

| Figure 3.  | Example Topologies                             |

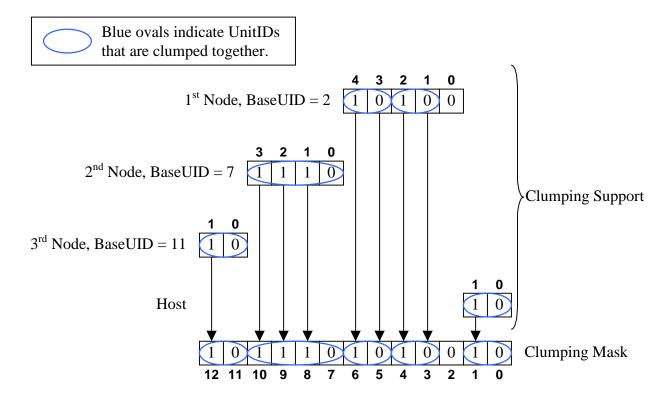

| Figure 4.  | Clumping Configuration                         |

| Figure 5.  | Example Data Buffer Sizing Calculation67       |

| Figure 6.  | Illustration of Packet History and Counters    |

| Figure 7.  | Example Retry Sequence                         |

| Figure 8.  | Receive FIFO                                   |

| Figure 9.  | Sync Sequence Timing for Link Initialization   |

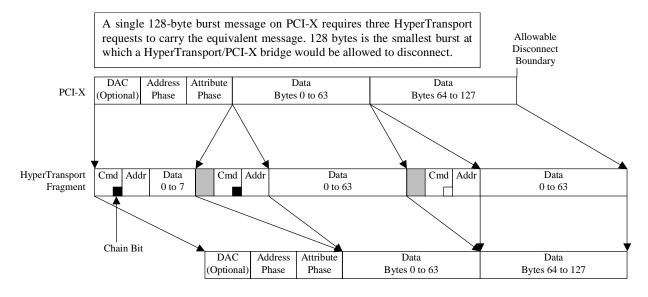

| Figure 10. | Fragment Use for PCI-X Messaging               |

| Figure 11. | I/O Space Aliasing                             |

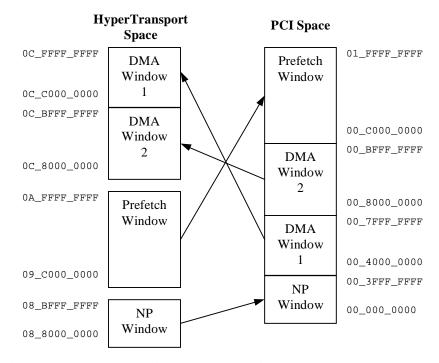

| Figure 12. | Memory Window Remapping                        |

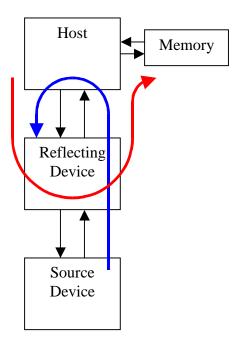

| Figure 13. | Reflection Example                             |

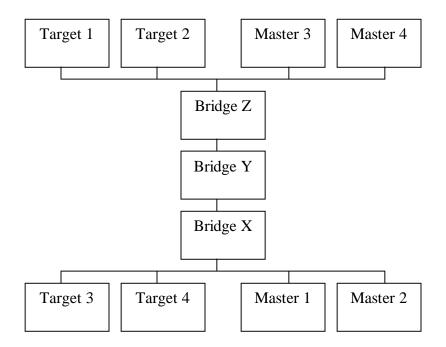

| Figure 14. | Example PCI System                             |

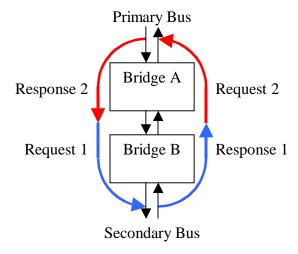

| Figure 15. | Request/Response Deadlock Loop                 |

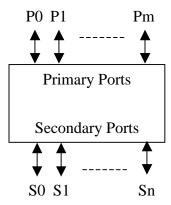

| Figure 16. | External Model of a Switch                     |

| Figure 17. | Logical Model of a Switch                      |

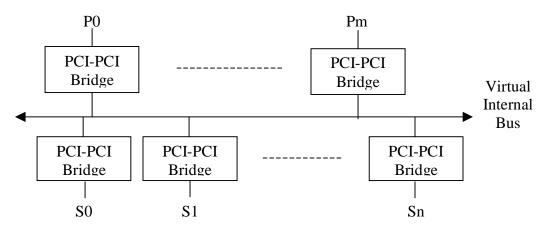

| Figure 18. | HyperTransport <sup>TM</sup> Link Interconnect |

| Figure 19. | DC Output Reference System Load                |

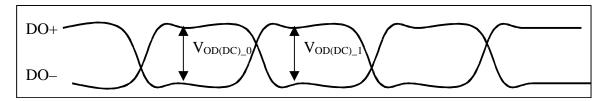

| Figure 20. | VOD(DC)                                        |

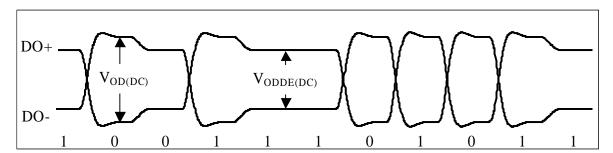

| Figure 21. | VODDE(DC)                                      |

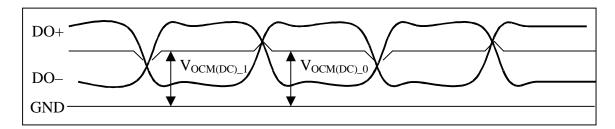

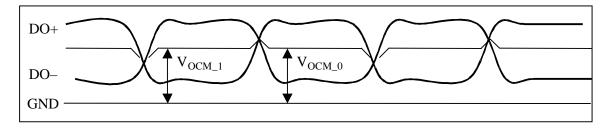

| Figure 22. | VOCM(DC)                                       |

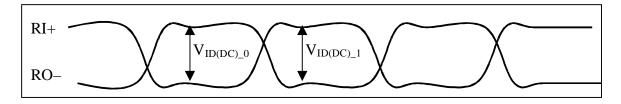

| Figure 23. | VID(DC)                                        |

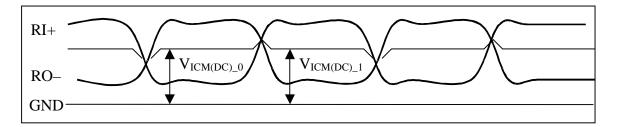

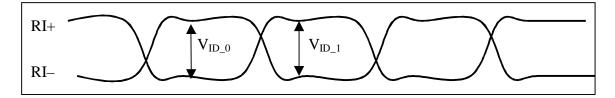

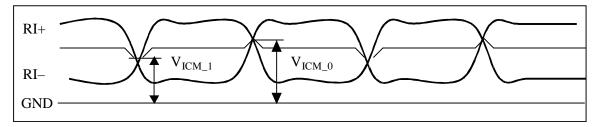

| Figure 24. | VICM(DC)                                       |

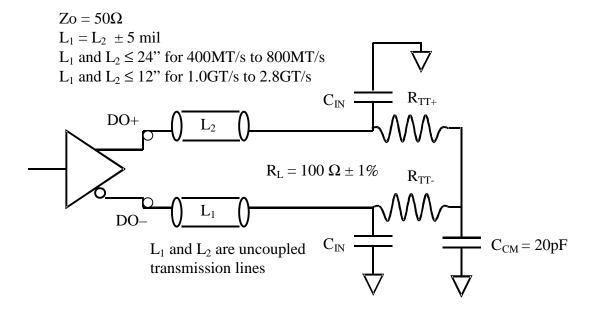

| Figure 25. | AC Reference System Load                       |

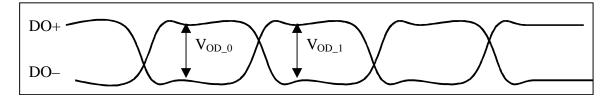

| Figure 27. | VOD AC                                         |

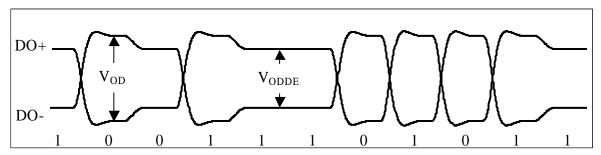

| Figure 28. | VODDE AC                                       |

| Figure 29. | VOCM AC                                        |

| Figure 30. | VID AC                                         |

#### HyperTransport™ I/O Link Specification Revision 2.00b

| Figure 31. | VICM AC           | 306 |

|------------|-------------------|-----|

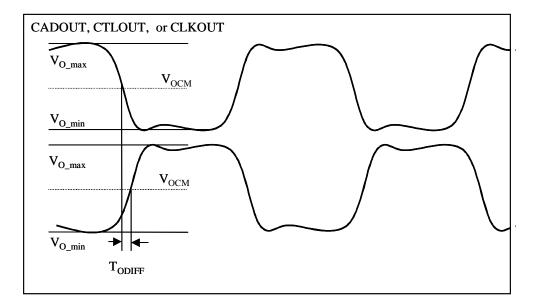

| Figure 32. | TODIFF            | 309 |

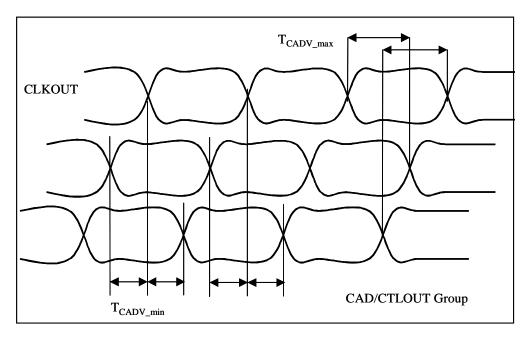

| Figure 33. | TCADV             | 310 |

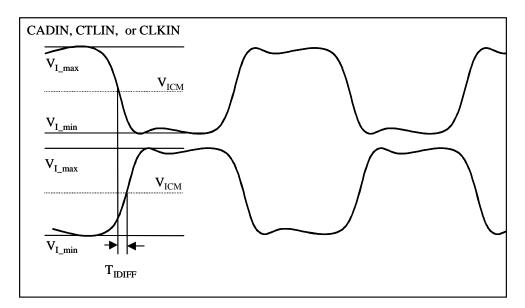

| Figure 34. | TIDIFF            | 311 |

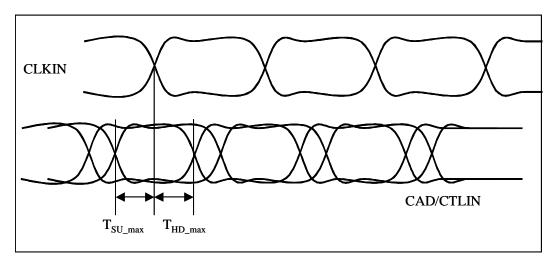

| Figure 35. | TSU and THD       | 312 |

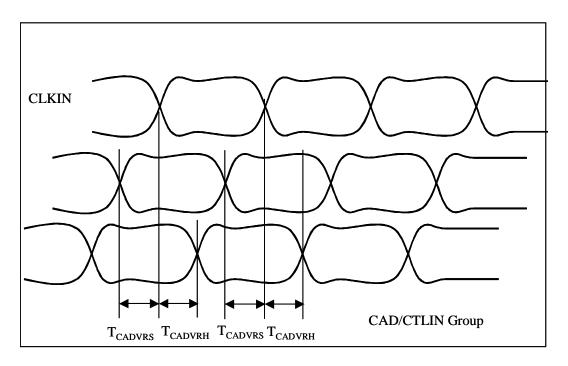

| Figure 36. | TCADVRS / TCADVRH | 313 |

$\textit{HyperTransport}^{\text{TM}} \textit{I/O Link Specification Revision 2.00b}$

# **List of Tables**

| Table 1.  | Link Signals                                        | 32 |

|-----------|-----------------------------------------------------|----|

| Table 2.  | Reset/Initialization Signals                        | 32 |

| Table 3.  | Power Management Signals                            | 33 |

| Table 4.  | Info Packet Format                                  | 37 |

| Table 5.  | Request Packet Format with Address                  | 37 |

| Table 6.  | Request Packet Format with Extended Address         | 38 |

| Table 7.  | Response Packet Format                              | 38 |

| Table 8.  | Command Field Encoding for All Control Packets      | 39 |

| Table 9.  | Eight-Byte Data Packet Format                       | 41 |

| Table 10. | Sized Byte Write Data Packet Format                 | 42 |

| Table 11. | UnitID Field Usage                                  | 47 |

| Table 12. | Sync Pattern Format                                 | 48 |

| Table 13. | Sized Read or Write Request Format                  | 49 |

| Table 14. | Broadcast Message Format                            | 51 |

| Table 15. | Flush Format                                        | 52 |

| Table 16. | Fence Format                                        | 53 |

| Table 17. | Atomic Read-Modify-Write (RMW) Request Format       | 54 |

| Table 18. | Request Packet Format with Extended Address         | 56 |

| Table 19. | Read Response (RdResponse) Packet Format            | 56 |

| Table 20. | Error bit encodings                                 | 57 |

| Table 21. | Target Done (TgtDone) Format                        | 58 |

| Table 22. | Virtual Channel Set Definitions                     | 61 |

| Table 23. | NOP Packet Format                                   | 67 |

| Table 24. | 4 Byte Extended Flow Control Packet                 | 68 |

| Table 25. | 8 Byte Extended Flow Control Packet                 | 69 |

| Table 26. | VCSetFree0 Definition for VCSet=0, the AltSet       | 69 |

| Table 27. | VCSetFreeX Definition for VCSet=2, the StreamVCs    | 69 |

| Table 28. | HyperTransport <sup>TM</sup> Technology Address Map | 79 |

|           |                                                     |    |

# HyperTransport<sup>TM</sup> I/O Link Specification Revision 2.00b

| Table 29. | Packet Ordering Rules                                                    | 84  |  |  |

|-----------|--------------------------------------------------------------------------|-----|--|--|

| Table 30. | Host Ordering Rules85                                                    |     |  |  |

| Table 31. | HyperTransport <sup>TM</sup> Technology Type 0 Address Format            | 89  |  |  |

| Table 32. | HyperTransport <sup>TM</sup> Technology Type 1 Address Format            | 89  |  |  |

| Table 33. | Extended HyperTransport <sup>TM</sup> Technology Type 0 Address Format   | 89  |  |  |

| Table 34. | Extended HyperTransport <sup>TM</sup> Technology Type 1 Address Format   | 90  |  |  |

| Table 35. | Extended HyperTransport <sup>TM</sup> Technology Software Address Format | 91  |  |  |

| Table 36. | HyperTransport <sup>TM</sup> Technology Device Header Format             | 92  |  |  |

| Table 37. | Memory Space BAR Format                                                  | 95  |  |  |

| Table 38. | I/O Space BAR Format                                                     | 96  |  |  |

| Table 39. | HyperTransport <sup>TM</sup> Technology Bridge Header Format             | 98  |  |  |

| Table 40. | Memory and Prefetchable Memory Base and Limit Register Format            | 100 |  |  |

| Table 41. | Prefetchable Memory Upper Register Format                                | 100 |  |  |

| Table 42. | I/O Base and Limit Register Format                                       | 101 |  |  |

| Table 43. | I/O Base and Limit Upper Register Format                                 | 101 |  |  |

| Table 44. | Slave/Primary Interface Block Format                                     | 105 |  |  |

| Table 45. | Host/Secondary Interface Block Format                                    | 105 |  |  |

| Table 46. | Command Register Format                                                  | 106 |  |  |

| Table 47. | Capability Type Encoding                                                 | 107 |  |  |

| Table 48. | Packet Forwarding Behavior                                               | 109 |  |  |

| Table 49. | Link Control Register                                                    | 110 |  |  |

| Table 50. | LDTSTOP# Tristate Enable Bit Encoding                                    | 113 |  |  |

| Table 51. | Link Configuration Register Definition                                   | 114 |  |  |

| Table 52. | Max Link Width In Bit Field Encoding                                     | 115 |  |  |

| Table 53. | Revision ID Register Definition                                          | 117 |  |  |

| Table 54. | Link Frequency Bit Field Encoding                                        | 118 |  |  |

| Table 55. | Link Error Register Definition                                           | 119 |  |  |

| Table 56  | Feature Capability Register Layout                                       | 120 |  |  |

| Table 57. | Error Handling Register Definition                                       | 122 |  |  |

| Table 58. | Interrupt Discovery and Configuration Capability Block Definition        | 126 |  |  |

|           |                                                                          |     |  |  |

# HyperTransport<sup>TM</sup> I/O Link Specification Revision 2.00b

| Table 59. | Interrupt Definition Registers                                  | 127 |

|-----------|-----------------------------------------------------------------|-----|

| Table 60. | 40 bit Address Remapping Capability Block Definition            | 128 |

| Table 61. | Secondary Bus Window Control Register Definition                | 129 |

| Table 62. | DMA Window Control Register Definition                          | 129 |

| Table 63. | 64 bit Address Remapping Capability Block Definition            | 130 |

| Table 64. | 64-bit Address Remap Indexed Registers                          | 131 |

| Table 65. | Revision ID Capability Block Definition                         | 132 |

| Table 66. | Clumping Capability Block Definition                            | 133 |

| Table 67. | Extended Configuration Space Access Capability Block Definition | 134 |

| Table 68. | MSI Mapping Capability                                          | 135 |

| Table 69. | DirectRoute Capability Block Definition                         | 136 |

| Table 70. | DirectRoute Indexed Registers                                   | 137 |

| Table 71. | VCSet Capability Block Definition                               | 138 |

| Table 72. | Retry Mode Configuration Registers                              | 140 |

| Table 73. | Retry Control Register                                          | 140 |

| Table 74. | Retry Status Register                                           | 141 |

| Table 75. | System Management Request WrSized Packet Format                 | 144 |

| Table 76. | System Management Request Broadcast Packet Format               | 144 |

| Table 77. | System Management Request Type Encoding                         | 144 |

| Table 78. | INTx Message Mapping at a Bridge                                | 148 |

| Table 79. | Interrupt Request Packet Format                                 | 151 |

| Table 80. | EOI Packet Format                                               | 152 |

| Table 81. | CRC Window Contents After Link Synchronization                  | 155 |

| Table 82. | CRC Values for Different Link Widths                            | 157 |

| Table 83. | Error Routing Registers                                         | 163 |

| Table 84. | CAD Value Driven by Transmitter Based on Receiver Width         | 181 |

| Table 85. | CAD Value Sampled for Transmitter and Receiver Width            | 182 |

| Table 86. | Signal States During Reset                                      | 182 |

| Table 87. | Values of CTL and CAD During Link Initialization Sequence       | 184 |

| Table 88. | Device Message Header Request Format                            | 189 |

|           |                                                                 |     |

# HyperTransport<sup>TM</sup> I/O Link Specification Revision 2.00b

| Table 89.  | Device Message Data Request Format                         |     |  |  |  |

|------------|------------------------------------------------------------|-----|--|--|--|

| Table 90.  | PCI-X, HyperTransport, and PCI Express Message Mapping     |     |  |  |  |

| Table 91   | Streaming Request Packet Format                            |     |  |  |  |

| Table 92.  | PCI Bus Transaction Ordering Rules                         |     |  |  |  |

| Table 93.  | PCI Transaction Mapping to HyperTransport Packets          | 202 |  |  |  |

| Table 94.  | HyperTransport Packet Mapping to PCI Transactions          | 203 |  |  |  |

| Table 95.  | HP AGP Transaction Mapping to HyperTransport Packets       | 204 |  |  |  |

| Table 96.  | Simple LP AGP Transaction Mapping to HyperTransport        | 205 |  |  |  |

| Table 97.  | Alternate LP AGP Transaction Mapping to HyperTransport     | 206 |  |  |  |

| Table 98.  | PCI-X Transaction Ordering Rules                           | 207 |  |  |  |

| Table 99.  | PCI-X Transaction Mappings to HyperTransport Packets       | 208 |  |  |  |

| Table 100. | PCI-X Completion Code Mappings to HyperTransport Encodings | 210 |  |  |  |

| Table 101. | HyperTransport Packet Mappings to PCI-X Transactions       | 210 |  |  |  |

| Table 102. | HyperTransport Error Mappings to PCI-X Completion Errors   | 212 |  |  |  |

| Table 103. | PCI MSI to HyperTransport Packet Mapping                   | 213 |  |  |  |

| Table 104. | PCI Express Transaction Ordering Rules                     | 214 |  |  |  |

| Table 105. | PCI Express Transaction Mappings to HyperTransport Packets | 215 |  |  |  |

| Table 106. | HyperTransport Packet Mappings to PCI Express Transactions | 217 |  |  |  |

| Table 107. | x86 Interrupt Request Packet Format                        | 235 |  |  |  |

| Table 108. | Destination Mode Bit Field Encoding                        | 236 |  |  |  |

| Table 109. | Trigger Mode Bit Field Encoding                            | 237 |  |  |  |

| Table 110. | Interrupt Request Bit Field Encoding Summary               | 237 |  |  |  |

| Table 111. | Standard End-of-Interrupt (EOI) Format                     | 238 |  |  |  |

| Table 112. | Redirection Table Format                                   | 239 |  |  |  |

| Table 113. | System Management Request Command Encoding                 | 243 |  |  |  |

| Table 114. | NOP Packet Format for Doubleword-Based Flow Control        | 251 |  |  |  |

| Table 115  | Switch Capability Block                                    | 276 |  |  |  |

| Table 116  | Streaming End-to-End Flow Control Request Format           | 286 |  |  |  |

| Table 117  | Message Flow Control Data Packet Format (first doubleword) | 287 |  |  |  |

| Table 118. | HyperTransport <sup>TM</sup> Link Signal Types             | 292 |  |  |  |

|            |                                                            |     |  |  |  |

#### HyperTransport™ I/O Link Specification Revision 2.00b

| Table 119. | HyperTransport <sup>TM</sup> Link Power Supply Characteristics             |     |  |  |

|------------|----------------------------------------------------------------------------|-----|--|--|

| Table 120. | Power Requirements                                                         |     |  |  |

| Table 121. | R <sub>TT</sub> and R <sub>ON</sub> DC Specifications                      | 296 |  |  |

| Table 122. | HyperTransport <sup>TM</sup> Link Differential Signal DC Specifications    | 299 |  |  |

| Table 123. | HyperTransport <sup>TM</sup> Link Single-Ended Signal AC/DC Specifications | 300 |  |  |

| Table 124. | AC Impedance Specifications                                                | 302 |  |  |

| Table 125. | HyperTransport <sup>TM</sup> Link Differential Signal AC Specifications    | 306 |  |  |

| Table 126. | Signal Groups for Transfer Timing                                          | 308 |  |  |

| Table 127. | HyperTransport <sup>TM</sup> Link Transfer Timing Specifications           | 313 |  |  |

| Table 129. | HyperTransport <sup>TM</sup> Link Phase Recovery Timing Characteristics    | 320 |  |  |

| Table 130. | Relationships Between AC and DC Parameters                                 | 323 |  |  |

| Table 131. | Relationships Between Output and Input Parameters                          | 323 |  |  |

| Table 132. | Package Skew                                                               | 324 |  |  |

| Table 133. | PCB Skew                                                                   | 325 |  |  |

HyperTransport<sup>TM</sup> I/O Link Specification Revision 2.00b

#### **Preface**

#### **This Document**

The *HyperTransport*<sup>TM</sup> *I/O Link Specification* defines and describes the input/output link protocol and electrical interface for the HyperTransport<sup>TM</sup> technology link. The document is divided into two principal parts: Protocol and Electrical. The protocol part includes information on HyperTransport technology signals, packets, commands, interrupts, configuration accesses, address map, error handling, clocking, and initialization. The electrical part includes information on I/O power supply, AC and DC characteristics, transfer timing, and phase recovery timing.

It is intended for system designers, circuit designers, sales and marketing engineers, and other technology professionals. This document serves as the primary reference for the HyperTransport protocol.

#### **Organization**

The document is divided into two sections, each with appendices.

Section 1 – Protocol

Section 2 – Electrical Interface.

# Section 1 – Protocol

#### 1 Overview

This document describes the HyperTransport<sup>TM</sup> technology I/O link. HyperTransport technology, formerly code-named Lightning Data Transport (LDT), is a packet-based link implemented on two unidirectional sets of signals. The link is packet-based, nominally point-to-point, and connects exactly two devices. Devices can have multiple HyperTransport links, allowing the construction of larger HyperTransport fabrics.

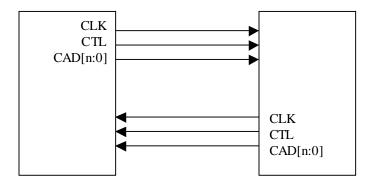

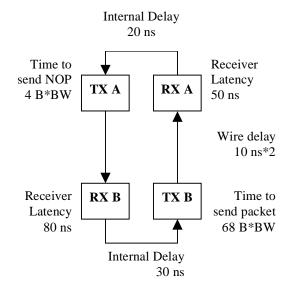

Figure 1. HyperTransport<sup>TM</sup> I/O Link

HyperTransport technology is used as an I/O channel, connecting chains of HyperTransport I/O devices and bridges to a host system. The interface from the host to the HyperTransport chain(s) is called the host bridge.

#### 1.1 Terminology

For reference, the following terms are used in the HyperTransport protocol:

- *Bit-time*—Half of a clock period in duration. Two data bits are transmitted on each signal per cycle.

- *Byte*—Eight bits.

- *Doubleword*—Four bytes.

- Quadword—Eight bytes.

- Packet—A series of bit-times that forms the basis of communication between two nodes.

- *Transaction*—A sequence of packets that are exchanged between two or more nodes in the system and that result in a transfer of information.

- *Source*—The node that initiates a transaction.

- *Target*—The node that ultimately services the transaction on behalf of the source. Note that there may be intermediary nodes between the source and the target.

- *I/O stream*—A collection of transactions that can be treated independently in the fabric with respect to ordering rules. A given I/O stream always originates from the same node and terminates at the same destination.

- *Unit* or *function*—A logical entity within a node that can act as a source or destination of transactions. Functions are useful for describing the transaction ordering rules of the HyperTransport protocol.

- *Node*—A physical entity that connects to one end of a HyperTransport link.

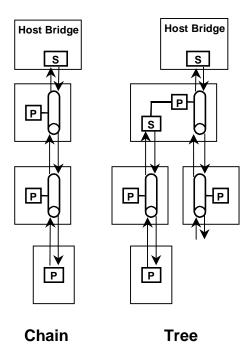

- *Chain*—A set of HyperTransport technology devices connected in a straight-line daisy-chain topology with each device connecting to at most two others. Devices with two link interfaces have no logical bridging function between the two interfaces; the entire chain operates as a single logical bus.

- Fabric—A HyperTransport I/O fabric is implemented as one or more daisy chains of HyperTransport technology devices, with a bridge to the host system at one end.

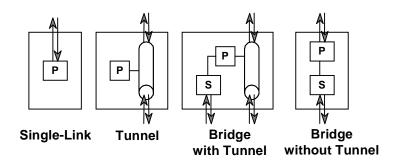

- *Bridge*—A device that bridges between a logical primary bus (connecting it to the host) and one or more logical secondary buses. It contains a bridge register set to control mapping of transactions between the two buses.

- *Tunnel*—A device that implements two link interfaces and is capable of forwarding traffic between other devices within a chain.

- *Cave*—A device that implements a single primary link interface.

- *Slave*—A tunnel or cave, implementing HyperTransport link(s) as its primary interface, not implementing the Host bridge functionality.

- *Host*—A host can contain multiple bridges, each supporting either a single HyperTransport chain or a tree of HyperTransport chains.

- Host bridge—The interface from the host to the HyperTransport chain.

- *Undefined*—Operations or behaviors that are described as undefined in this specification may result in any outcome from no change in the state of the system to creating an environment in which the system no longer continues to operate. Note that a cold reset of the HyperTransport fabric may not be sufficient to restore deterministic operation since the effects of an undefined action may propagate beyond the HyperTransport fabric.

- *CSR*—Configuration Space Register

#### 1.2 HyperTransport<sup>TM</sup> Technology in x86 Platforms